Back to Menu

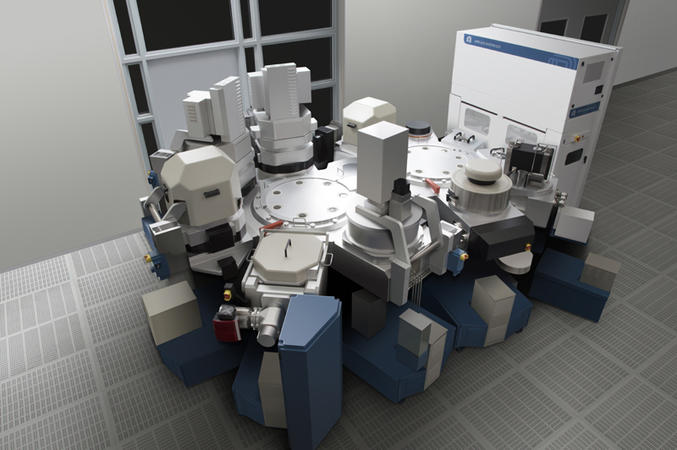

Endura® Cirrus™ HT CO PVD

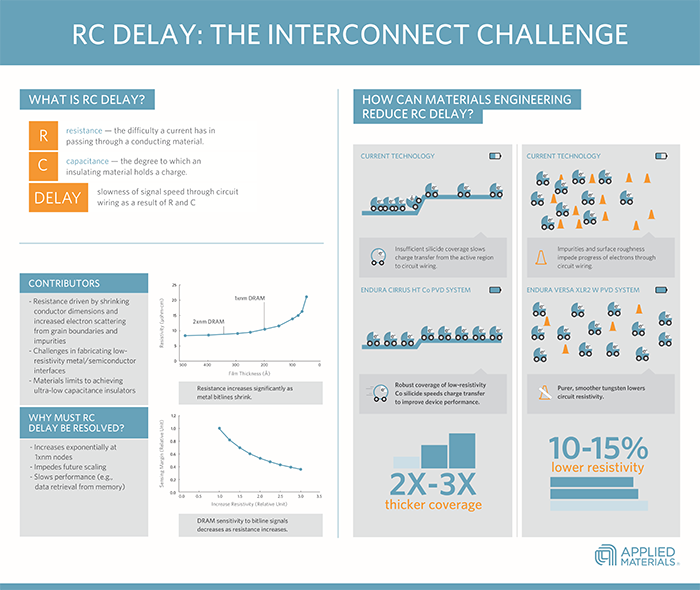

集積回路と他のコンポーネントのスケールダウンが進むに連れ、メタル配線とコンポーネント間のコンタクトも縮小しています。結果として、これらのコネクタにおける抵抗が増大しています。さらなる微細化を実現し、よりコンパクトで速い電子デバイスを達成するためには、抵抗は最低限に抑えられなければなりません。

遅延効果を引き起こす、より高い抵抗は多くの場合、抵抗容量遅延(RC遅延)と呼ばれ、回路にさまざまな影響を及ぼします。好ましくない影響のつとして、RC遅延はビットラインを通じてDRAM構造へのデータの書き込み、読み込みを減速させる可能性があります。加えて、より高い抵抗は、より高い消費電力につながり、モバイル技術に好ましくない副作用を与えます。

微細化の他の副産物としては、先進の回路においてフィーチャー密度が増すに連れ、アスペクト比が増大していくことです。このため、最終デバイスで適切な電気的性能を達成するために必要なボトムカバレージで成膜することが、より困難になってきています。DRAM構造で特に重要なのは、活性領域とメタル配線の最初の層における、半導体とメタル界面です。これらの界面において、迅速かつ最大限の電荷移動を達成するために、低抵抗のCoシリサイドが使用されます。この効果は、適切な厚みと均一な界面層の成膜に依存します。

Endura Cirrus HT Co PVDシステムは、コンタクト領域の縮小やアスペクト比の増大といった課題を克服する機能強化を通じて、要求されたシリサイドカバレージを提供します。高周波RF源を採用することで、他のあらゆるソース技術よりも高密度のメタルイオンを含んだプラズマを生成し、 同システムは高アスペクト比フィーチャーの底部において、優れた厚みと均一性を達成します。ウェーハ上の負電圧は、陽メタルイオンを狭いホールに導きます。より多くのメタルイオンが生成されるため、高アスペクト比のコンタクトホール底部のカバレージは、現行の技術で生成するよりも2〜3倍の厚みがあります。結果として、メタルと半導体の電荷移動の障壁を低下させる、強固なCoシリサイド膜が形成されます。

同システムは、DRAM周辺のダイレクトコンタクトアプリケーション向けに、Siconiプリシリサイドクリーン技術とPVDコバルト、TiNキャップ成膜を統合しています。

オーミックコンタクトの課題

メモリデバイスでは、オーミックコンタクト(半導体とメタル界面)が活性領域とメタルワイヤを接続します。メモリの微細化が進むに連れ、オーミックコンタクトの領域はテクノロジーノード間で約70%縮小します。一方で、このコンタクトを作成するために、低抵抗のシリサイドを成膜しなければならず、アスペクト比は増大していきます。1xnm DRAMでは、これら2つの要素により、電荷が活性領域からコンタクトを通って上部レベルのワイヤへと移動し、また戻ってくる際に迅速かつ確実に移動できるように、Coシリサイド膜に十分な厚みを持たせることが非常に困難になってきています。

次のアニメーションは、オーミックコンタクトのコンセプトとEndura Cirrus HT Co PVDシステムによって生成された厚いシリサイドカバレージが、いかにデバイス性能に有益な影響をもたらすかを示すものです。

RC遅延は、今日の多機能なコンシューマー向けモバイル電子機器の性能向上を牽引する、ロジックやメモリデバイスのさらなる微細化を継続する上で、重大な障壁となる可能性があります。

ロジックおよびメモリチップにおけるアクティブデバイス(トランジスタ)では、各デバイスとチップの他の領域が金属製のワイヤで電気的に接続されています。これらのワイヤはそれぞれが、非導電(絶縁)の誘電体層によって隔離されています。ロジックおよびメモリチップにおける配線の役割は、チップ上の1つの領域から他の領域へと、信号を送信することです。縮小していくジオメトリにて、信号ロスを最低限に抑えつつ、この信号の送信を可能な限り迅速に行う能力が、デバイスの微細化において非常に重要です。ロジックでは、微細化とは領域の微細化を意味します。すなわち、材料や設計の革新により、より多くの回路をより小さな領域に詰め込んでいくことです。コスト要求の厳しいDRAMの製造では、コストは厳しく管理されなければなりません。このため、既存の材料や設計でより高い性能を得ることに注力した微細化が必要になります。一般的に、ロジックおよびメモリワイヤの信号伝達速度は、一様に基本的な原則に則っており、製品の抵抗容量(RC)に依存します。抵抗と容量を同時に低下することが理想です。しかし、より低容量の絶縁材料を開発し、製造工程に統合することは、特にメモリの生産においては非常にコスト高になります。ゆえに、性能の拡張には抵抗率を下げることが望ましいアプローチとなります。電荷が配線の異なる層を垂直に移動するのか、導体の長さに沿って移動するのかにより、RCの課題解決には異なるソリューションが必要です。いずれの場合でも、メタルワイヤの抵抗率を下げることが目標となります。垂直形状の場合は、界面抵抗を最小限に抑えることを目的とします。電気コンタクトはデバイスの活性領域をメタルワイヤの最初の層に接続します。半導体とメタル界面(もしくはオーミックコンタクト)は活性領域とメタルコンタクトの接点を形成します。目的は、電荷がコンタクトを通って上層部のワイヤに確実に移動し、また戻ってくることができるようにすることです。オーミックコンタクト全体で迅速かつ最大限の電荷移動を達成するために、低抵抗の材料が形成されます。このために、低抵抗のCoシリサイドが業界標準として採用されました。この効果を十分に発揮するためには、堅牢なオーミックコンタクトを形成する均一な成膜が必要です。側面形状では、ワイヤを形成するメタルの導電性を最適化することを目的とします。ライン抵抗は文字通り、ワイヤ形状(幅、高さ、長さ)とワイヤ製造に使用される特定の材料(通常タングスタンや銅)の特性、双方の機能を示します。配線の抵抗率を下げる最も簡単な方法は、導電金属の分量を増やすこと、例えば、ワイヤの幅を広く、高くすることです。しかし、幅広いワイヤは微細化の制限につながり、高いワイヤは静電容量が増大し、エッチングが困難になります。結果として、最先端のデバイスでは、ワイヤの抵抗値を下げるために、DRAMビットラインのケースではタングステン(W)といった、導電材料の改善に注力しています。ENDURA® Versa™ XLR2 W PVDの詳細。