半导体 (Semiconductor)

解决方案与软件

DRAM 剖析

动态随机存取存储器(DRAM)是一种计算机组件,处理器在其中快速存储每秒进行数十亿次计算所需的信息。 典型的 DRAM 芯片有三个主要区域:

- 电池阵列,单个比特存储在微小的电容器中;

- 逻辑区或核心区,感测放大器和字线解码器等设备在此帮助确定如何从单元阵列中获取数据;

- 外围设备,构成进出 DRAM 芯片的通信链路。

为满足业界对 DRAM 性能不断增加的要求,这三个区域都要进行微缩。这些缩放要求包括最大限度地提高电容器中可存储的电荷量、减少感应放大器的变化以及降低电路布线造成的功率损耗。

外围逻辑器件微缩

DRAM 单元中的数据由外围逻辑器件管理。外围电路主要包括高速逻辑晶体管和连接 DRAM 各部分的布线。要保持 DRAM 单元中存储的信息的完整性,就必须最大限度地提高通向该电路的信号。 要保持 DRAM 单元中存储的信息的完整性,就必须最大限度地提高通向该电路的信号。

许多 DRAM 制造商一直在用高介电材料取代聚硅氧烷介电质,用金属栅极取代多晶硅栅极,以提高晶体管的性能。当几种不同的薄膜逐层沉积时,薄膜及界面的任何缺陷都会对电子传输的工作方式产生很大影响。

应用材料公司为 DRAM 后端铜线 提供业界领先的低介电常数产品 Black Diamond™ ,以有效解决外围逻辑微缩问题。Black Diamond 可将介电常数降低 25%。通过采用我们的 Endura CuBS 产品 和CVD 钴, 后端铜金属化的可靠性提高了 10 倍以上 。在电流密度较高的情况下,使用钴封盖有助于减少铜电迁移。

DRAM 堆栈--微缩

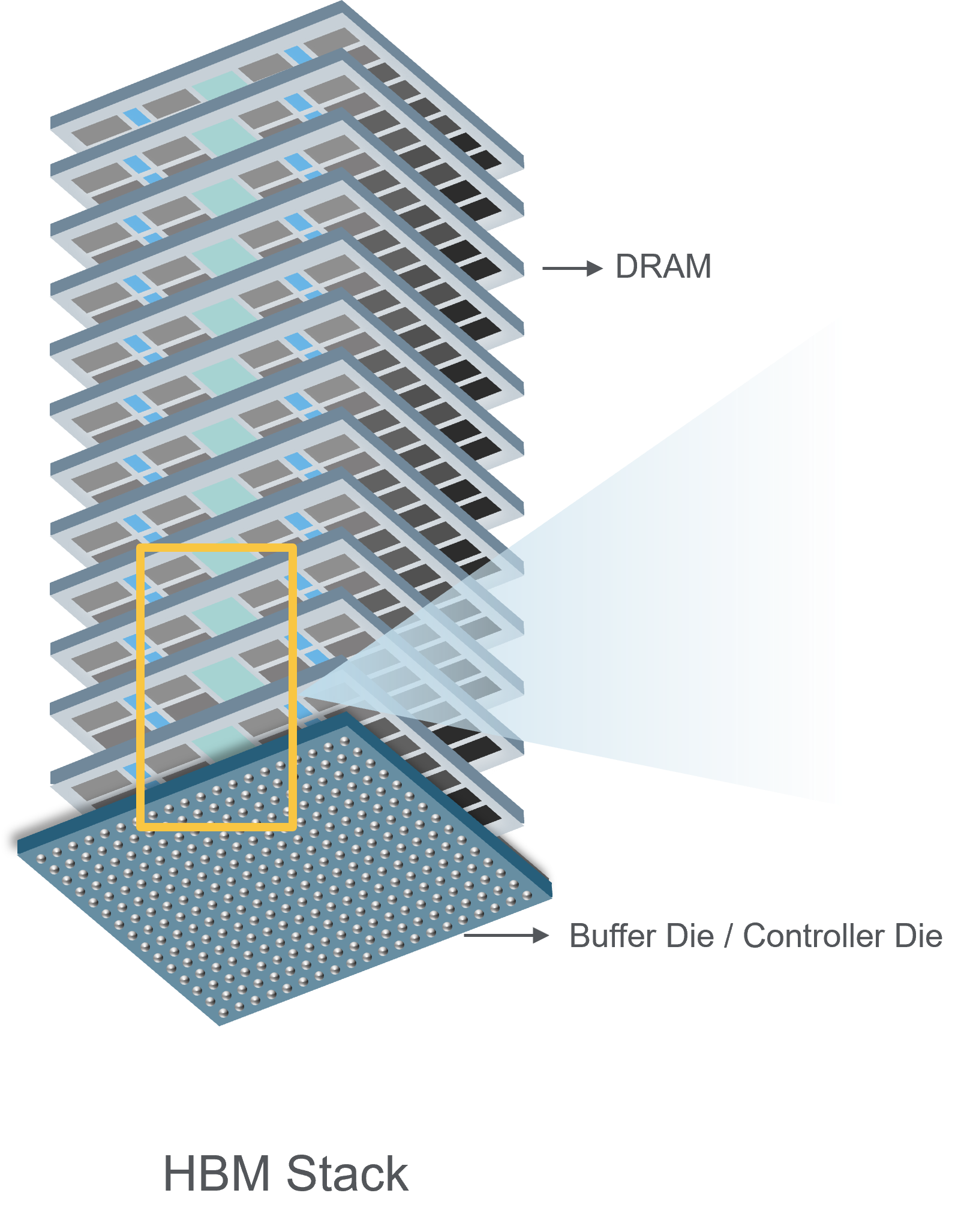

为了提供人工智能应用所需的大量内存,芯片制造商已转向高带宽内存(HBM)--一种由先进 DRAM 堆叠而成的高性能、低延迟架构。DRAM 芯片的创新固然重要,但 HBM 背后的密度和带宽是通过先进的 3D 封装实现的。 应用材料公司是材料工程技术领域的领军企业,其所需的材料工程技术可为业界日益增多的 HBM 应用提供支持。 点击此处了解更多。

垂直微缩 - 3D DRAM

3D DRAM 是指在垂直方向上存储比特的架构,类似于 3D NAND。然而,DRAM 的速度几乎是 NAND 的 1000 倍,它是通过使用高迁移率硅衬底作为形成通道的起始材料来实现这一速度的。 DRAM 的高速度还来自于电荷可以快速进出电容器。 随着 DRAM 向垂直方向扩展,需要创新材料来实现高迁移率和超低缺陷沟道。

应用材料公司在用于沉积高迁移率材料的新材料创新技术方面处于领先地位,这些技术包括外延生长、PVD 和 ALD。一旦沉积完成,这些薄膜将被刻蚀以进入底层。3D DRAM 预计需要先进的间隙填充、 选择性去除 和先进的掺杂能力。这些功能必须无缝集成,才能实现成功的解决方案。我们在开发集成材料解决方案™ 以协同优化这些不同工艺方面的领先地位,也将是为 3D DRAM 必将面临的集成挑战提供整体解决方案的关键因素。