Back to Menu

製品情報

半導体

市場と変化

ソリューションとソフトウェア

DRAMのアナトミー

ダイナミックランダムアクセスメモリ(DRAM)は、プロセッサが毎秒何十億もの計算を実行するために必要な情報をすばやく保存するコンピュータコンポーネントです。 一般的なDRAMチップには、主に3つの領域があります。

- セルアレイでは、個々のビットが小さなコンデンサに格納されています。

- ロジック領域またはコア領域では、センス・アンプやワード・ライン・デコーダなどのデバイスが、セル・アレイからデータにアクセスする方法を決定するのに役立ちます。

- DRAMチップの内外に通信リンクを形成する周辺部。

これら3つの領域は、業界で増え続けているDRAM性能要件に合わせて拡張しなければなりません。これらのスケーリング要件には、コンデンサに蓄えることができる電荷の最大化、検出アンプの変動性の低減、回路内の配線による電力損失の低減が含まれます。

セルアレイのスケーリング

データが記憶されるDRAMセルアレイは、ダイの最も大きな部分であり、単位面積内のセル数を増やすことで、ダイの密度を高めることができる。 これを実現するには、セルコンデンサとトランジスタの寸法を小さくする必要があります。 これは、ゲートピッチとビットラインピッチの低減だけでなく、DRAMセルのスケーリングに役立ちます。

周辺ロジックのスケーリング

DRAMセル内のデータは、周辺ロジックデバイスによって管理されます。周辺回路は、主に高速ロジックトランジスタと、DRAMのさまざまな部分を接続する配線で構成されています。 この回路への信号を最大化することは、DRAMセルに保存された情報の完全性を維持するために重要です。

多くのDRAMメーカーは、トランジスタの性能を向上させるために、ポリSiON誘電体をhigh-k材料に、ポリシリコンゲートを金属ゲートに置き換えています。複数の異なる膜を交互に積み重ねた場合、膜や界面に欠陥があれば、電子伝達の機能状態に大きく影響します。

アプライド マテリアルズは、DRAMバックエンド銅配線向けに業界をリードする低誘電率誘電体製品Black Diamond™を提供し、周辺ロジックのスケーリングに効率的に対応します。Black Diamond™は誘電率を25%低減します。CVDコバルトとともにEndura CuBS製品を採用することで、バックエンド銅メタライゼーションの信頼性が10倍以上も向上しました。コバルトキャッピングを使用すれば、より高い電流密度で銅エレクトロマイグレーションを低減できます。

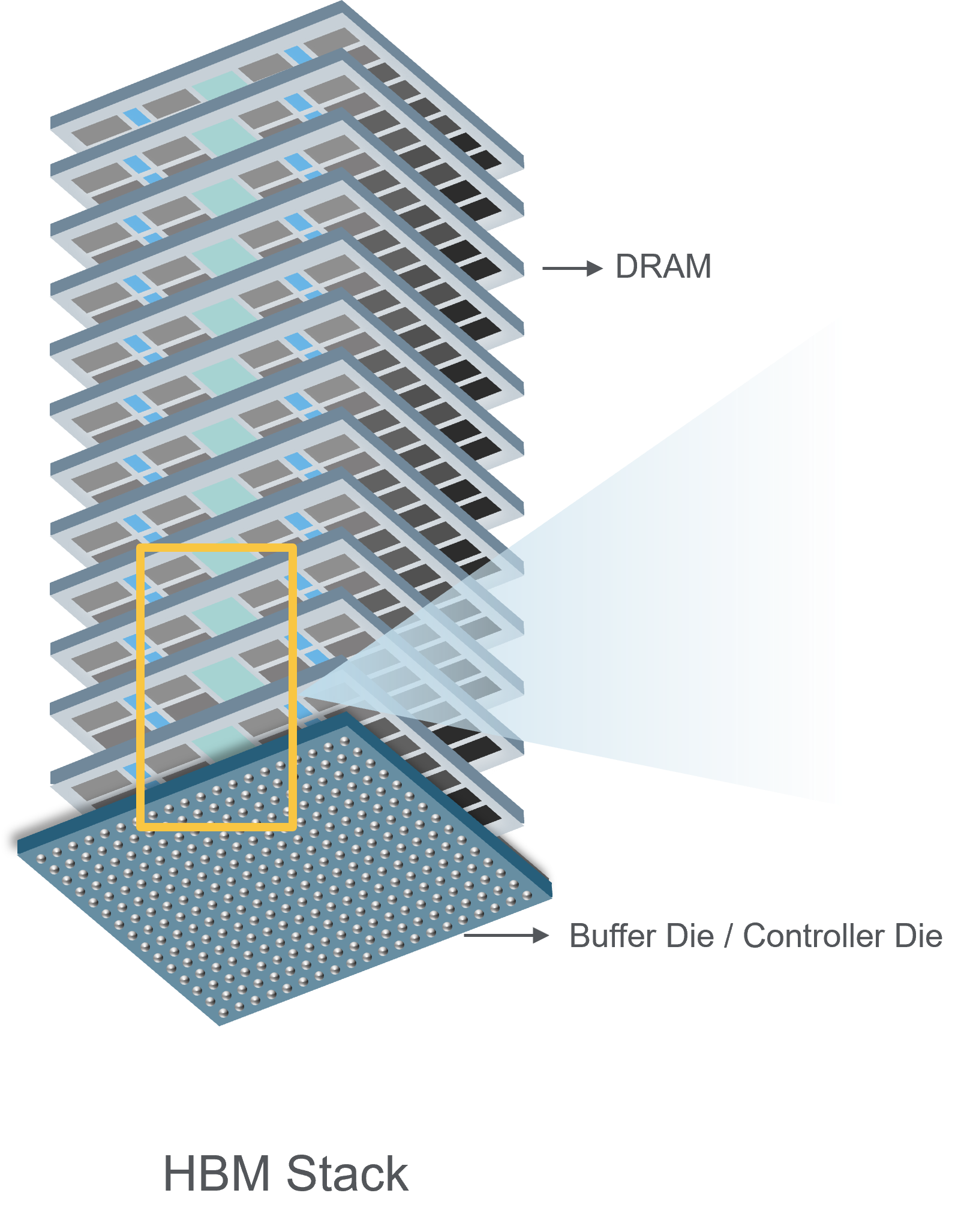

DRAMスタッキング – HBM

AIアプリケーションに必要な大容量のメモリを提供するため、チップメーカーは、高性能で低レイテンシーのアーキテクチャを先端DRAMの積層で構築している、高帯域メモリ(HBM)に目を向けてきました。 DRAMチップにおける技術革新は重要ですが、HBMの背後にある密度と帯域幅は、高度な3Dパッケージングによって実現されます。アプライド マテリアルズは、HBMの導入が進む業界を支える材料エンジニアリング技術のリーダーです。続きを読む

垂直スケーリング – 3D DRAM

3D DRAMとは、3D NANDと同様に、垂直方向でのビットのアーキテクチャ格納を指します。しかし、DRAMの速度はNANDのほぼ1000倍です。この速度は、出発原料として高移動度シリコン基板を使用してチャネルを形成することで実現されています。DRAMの高速性は、電荷がコンデンサにすばやく出入りできることにも起因しています。 DRAMが垂直方向に拡張されるにつれて、高移動度と超低欠陥チャネルを実現するための新しい材料の革新が必要とされています。

当社独自のVolaris™ プレクリーン技術と業界をリードするバンプ下メタライゼーションPVDの組み合わせにより、バンプの信頼性を向上させながら、接触抵抗と寄生電力を低減することができます。成膜後、これらの膜をエッチングして下層にアクセスします。3D DRAMには、高度なギャップフィル、選択的除去、先進のドーピング機能が必要になると考えられます。ソリューションを成功させるには、これらの機能をシームレスに統合する必要があります。また、これらのさまざまなプロセスを協調最適化するためのインテグレーテッド マテリアルズ ソリューション™開発における当社のリーダーシップも、3D DRAMが直面する統合問題に対して包括的なソリューションを提供できることから、重要なイネーブラーとなります。