Back to Menu

製品情報

半導体

市場と変化

ソリューションとソフトウェア

高帯域メモリ (HBM)

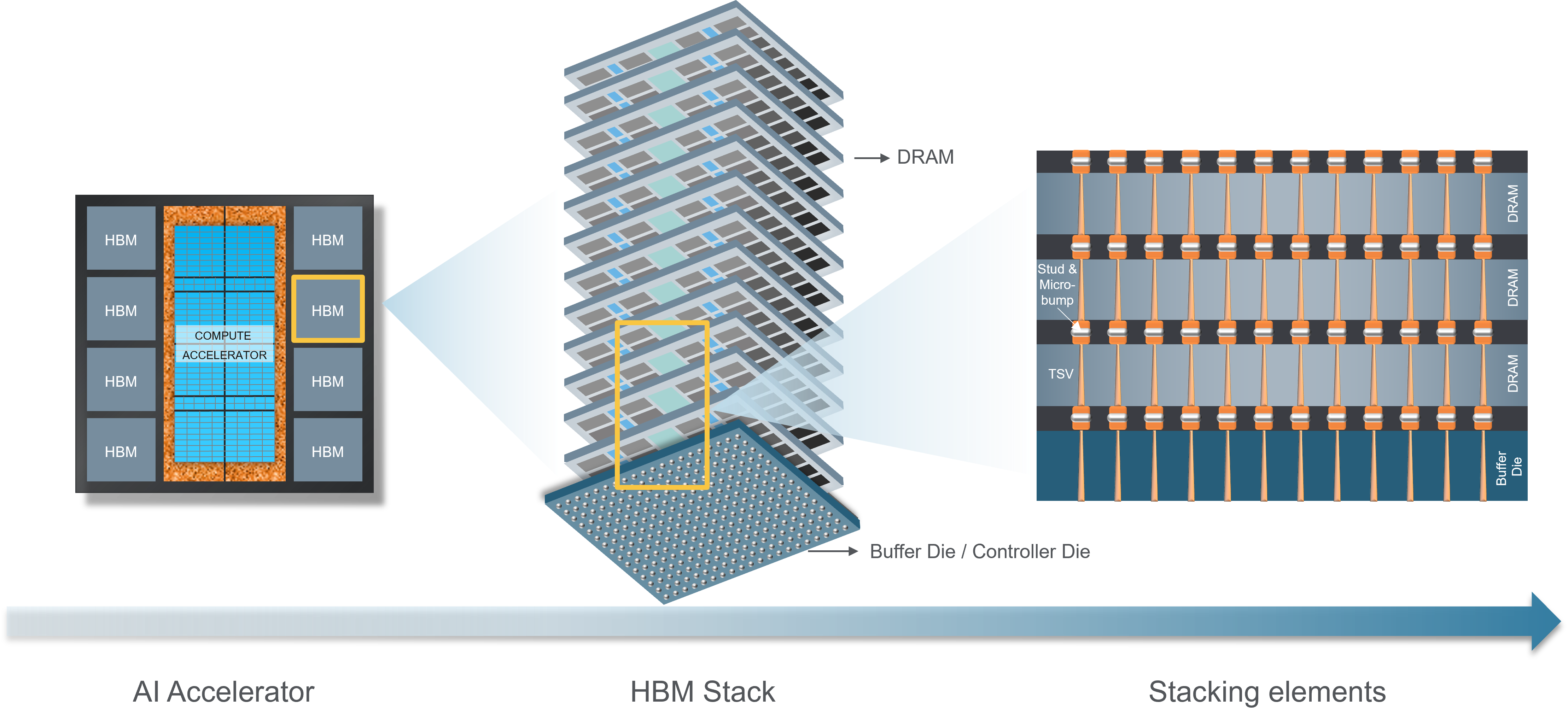

AIアプリケーションに必要な大容量のメモリを提供するため、チップメーカーは、高性能で低レイテンシーのアーキテクチャを先端DRAMの積層で構築している、高帯域メモリ(HBM)に目を向けてきました。DRAMチップにおける技術革新は重要ですが、HBMの背後にある密度と帯域幅は、高度な3Dパッケージングによって実現されます。アプライド マテリアルズ®は、HBMの採用が進む業界を支えるマテリアルズ エンジニアリング技術のリーダーです。

HBMの製造フローでは、ウェーハの表裏両面にピラー配線やシリコン貫通ビア(TSV)を形成するなど、多くの重要なマテリアルズ エンジニアリングの工程が必要となります。

アプライド マテリアルズは、より高いアスペクト比のTSVを実現し、ビアトレンチ内のカバレッジを向上させる誘電体および金属の成膜技術を開発しました。当社のProducer™ InVia™ 2 CVD システムは、ビア側壁の形状に正確に沿った均一な誘電体ライナーの低温成膜を可能にする独自のプロセスを採用しています。同様に、当社のEndura™ Ventura™ 2 PVD システムは、金属堆積の制御性を高め、バリアシード層の良好なカバレッジを確保し、より高い電気性能と信頼性を実現します。

TSV以外にも、マイクロバンプピラーはHBMスタックの電気的および熱的性能にとって重要です。マイクロバンプの寸法とピッチを縮小する技術革新は目覚ましいですが、バンプとそれに対応するボンドパッドが縮小するにつれて、接触抵抗は指数関数的に増大します。当社独自のVolaris™ プレクリーン技術と業界をリードするアンダー・バンプ・メタライゼーションPVDの組み合わせにより、バンプの信頼性を向上させながら、接触抵抗と寄生電力を低減することができます。アプライド マテリアルズのNokota™ ECDと連携することで、当社は大手顧客のマイクロバンプ製造において重要なポジションを獲得しています。

HBMプロセスにおけるもう一つの大きな課題は、非常に薄いダイの積層です。これはダイの反りや曲がりによって妨げられる可能性があります。当社のProducer™ Avila™ PECVD システムは、ウェーハの裏面に薄い誘電体膜を低温で成膜するため、チップメーカーは膜の応力を調節して反りを制御することができます。