Back to Menu

Producer® Selectra® Etch

Producer Selectra Etch 시스템은 3D 로직 및 메모리 칩의 추가 미세화를 통해 무어의 법칙의 모멘텀을 유지하는 유례 없는 기능을 제공합니다. 이 공정은 하나 이상의 필름에 대한 뛰어난 선택비로 표적 물질을 제거할 수 있습니다.

차세대 집적 회로에서는 칩 설계의 형상이 더 작아지고 종횡비가 더 커지고 패킹 밀도가 더 높아지고 있습니다. 궁극적인 신뢰도와 성능을 위해서는 소자의 정확한 패터닝 또는 세정이 중요합니다. 불충분한 선택비로 인한 재료의 불완전한 제거 또는 임계 치수의 증가는 소자 성능과 수율에 결정적인 영향을 미칠 수 있습니다. 또한 고종횡비 형상의 패턴 변형(라인 굽힘, 패턴 붕괴)이 차세대 소자의 수율에 영향을 미칠 수 있습니다.

Selectra 시스템은 이러한 각각의 문제를 해결합니다. 이 고유한 공정은 차세대 FinFET에 대해 원자 수준의 식각 제어, 3차원 수직 구조 낸드에 대해 균일한 리세스, 고종횡비 DRAM 구조에 대해 무손상 세정을 구현합니다.

이 시스템은 래디컬 기반의 화학 반응을 사용해 원자 수준의 정확도로 다양한 유전체, 금속, 반도체 필름을 제거하기 위한 조절 가능한 선택비를 구현합니다. 이 기술은 오늘날의 FinFET 소자의 경계를 확장해서 무어의 법칙을 전진시키고 미래의 전면 게이트 구조를 구현하는 데 필수입니다.

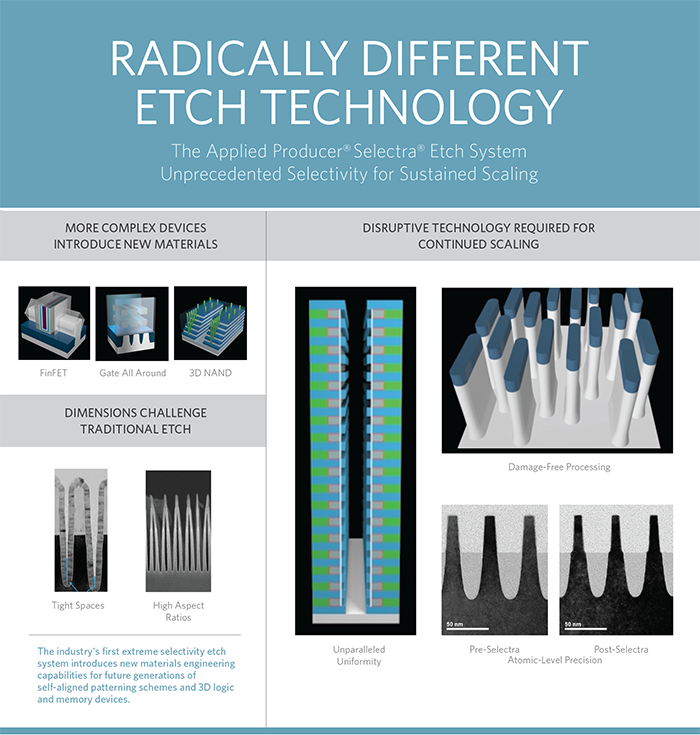

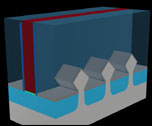

종래 공정은 선택비가 불충분하기 때문에 NAND 스택의 바닥보다 꼭대기 근처에서 텅스텐의 움푹 파임 현상이더 커져서 소자 성능이 떨어지게 됩니다.

재료 선택비가 부족하면원통형 DRAM 커패시터의모든 층을 넓게 만드는 습식 식각 화학 반응이 발생해 원하지 않는 지름 증가가 발생합니다.

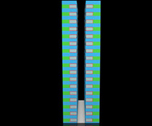

결정면에 의존하는 습식 식각 공정의 결과로차세대 로직 트랜지스터의 작은 공간에폴리실리콘 잔류물이 남게 됩니다.

습식 식각 이후의 건조 단계중에 모세관 작용력("정적 마찰력")이고종횡비 형상의 붕괴를 초래합니다.

Selectra 공정은 텅스텐 선택비를조절할 수 있어 전체 3차원 수직 구조 낸드 스택에서 매우 균일한 리세스 식각을 구현할 수 있습니다.

Selectra 공정은 원통 지름이 넓어져야 하는 층에서만선택적으로 작용하도록 조절할 수 있습니다.

Selectra 공정은 폴리실리콘 잔류물의 흔적을모두 제거하여 게이트 산화막을

청결하게 유지하고 금속 게이트 증착이 가능하도록 합니다.

완전 건식 Selectra 공정은 취약한 형상의구조적 무결성을 보존합니다.

- 1 / 5

- 2 / 5

- 3 / 5

- 4 / 5

- 5 / 5