半导体 (Semiconductor)

解决方案与软件

异构集成

几十年来,半导体行业一直依赖二维微缩和单片半导体集成来不断推进,这可以同时改善芯片性能、功率和面积/成本。但是,随着二维微缩的放缓和成本的提高,芯片制造商越来越多地转向异构设计以及芯粒和器件的封装内集成,以改善功率、性能、面积、成本和上市时间(PPact™)。

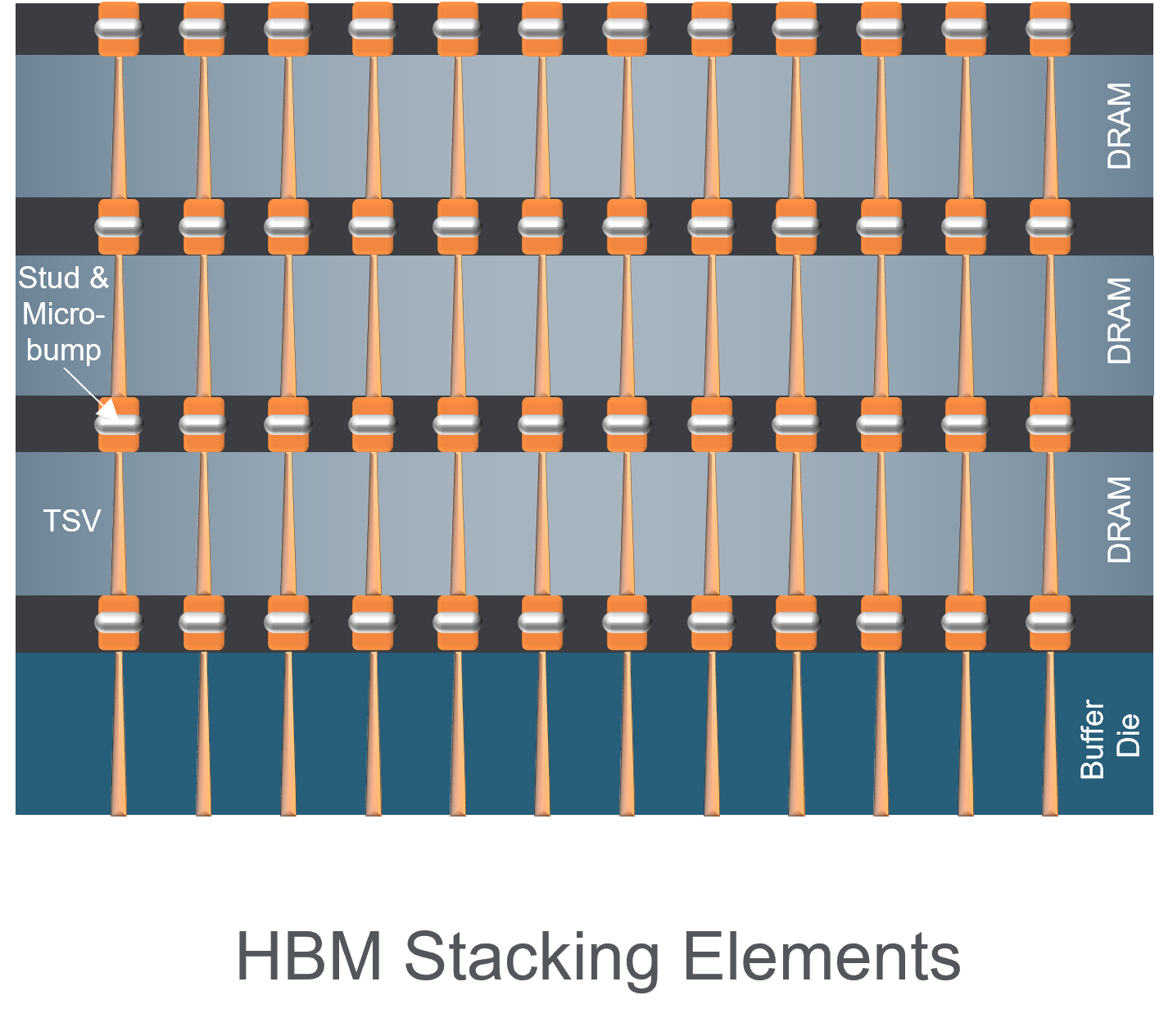

当大型机和个人电脑在电子行业占据主导地位时,封装的主要作用是保护硅芯片和连接印刷电路板(PCB)。当时使用的主要技术是线键合。封装凸点 允许在两个平行面之间进行多重连接。必要时,扇出 可重新定位连接点,特别是从晶粒上非常紧凑的间距到 PCB 上更宽松的间距。某些器件采用了硅通孔 (TSV),可实现芯片到芯片的直接连接。所有这些创新都提高了封装密度,实现了更高的速度和更低的功耗。

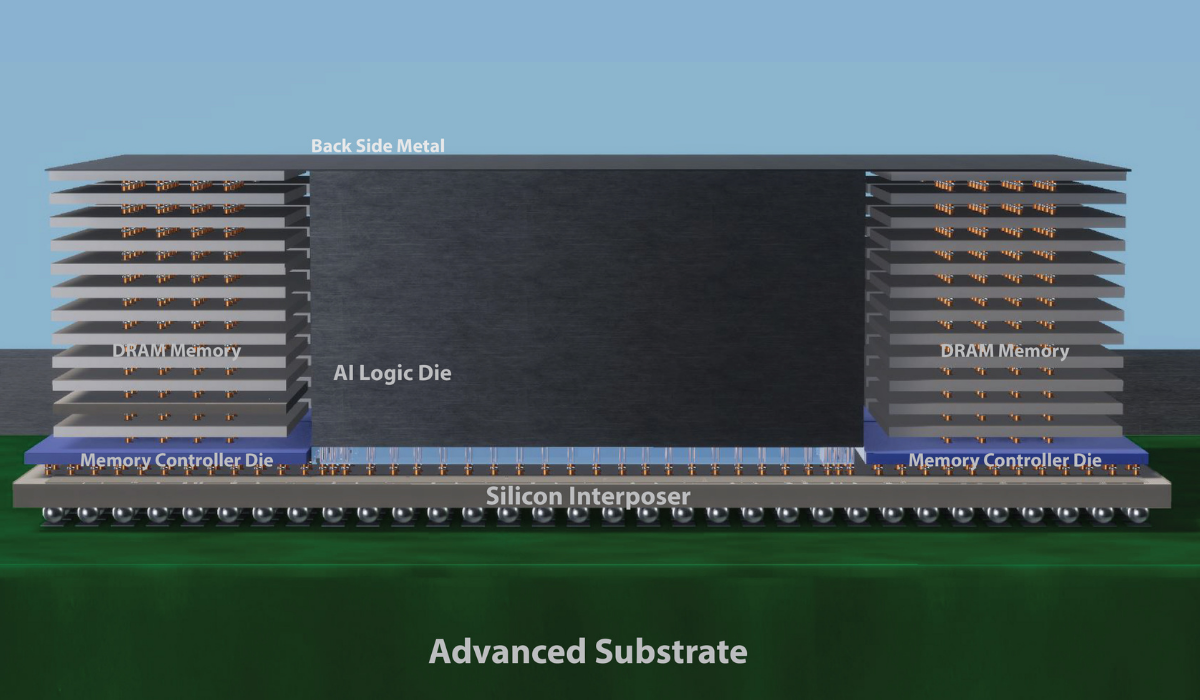

设计人员希望以更低的功耗获得更高的系统级性能,这促使他们考虑如何以最佳方式集成芯片和系统。设计人员发现,很难在单个晶粒上放置高性能计算、机器学习和其它人工智能工艺所需的晶体管。作为替代方法,设计人员正在使用多晶粒先进封装,使高性能逻辑芯片和存储器更加接近,从而降低延迟和功耗。这种被称为异构集成的方法需要极高密度的短连接,比以往的封装技术高出几个数量级。

转向异构集成需要两大突破:

- 首先是混合键合,芯片和晶圆可直接通过铜来连接。

- 随着越来越多的芯粒集成到单个封装中,封装的尺寸更大,也更加复杂。业界正在从硅晶圆衬底转向更大的先进衬底。

异构设计对世界领先的半导体和系统公司要实现 PPACt 路线图而言越来越重要。通过我们在业界领先的产品组合上的独特广度和深度,以及行业合作关系,和世界领先的晶圆级封装实验室,在这里与客户和行业伙伴共同创新,应用材料公司正在帮助加速这一趋势。