Back to Menu

製品情報

アプライド マテリアルズ コンピューティングのエネルギー効率を高める革新的なチップ配線技術を発表

- 業界で初めてルテニウムを量産採用、銅配線の2nm以降への微細化と最大25%の低抵抗化を実現

- 新改良のLow-k絶縁材料でチップキャパシタンスを低減、3D積層ロジック/DRAMチップを高強度化

アプライド マテリアルズ(Applied Materials, Inc., Nasdaq:AMAT、本社:米国カリフォルニア州サンタクララ、社長兼CEOゲイリー・E・ディッカーソン)は7月8日(現地時間)、銅配線を2nmロジックノード以降へと微細化してコンピューティングシステムのワットあたり性能を高める、画期的なマテリアルズ エンジニアリング技術を発表しました。

アプライド マテリアルズのセミコンダクタプロダクトグループ プレジデント、プラブー・ラジャ(Prabu Raja)は次のように述べています。「AI時代を迎えてコンピューティングのさらなるエネルギー効率化が求められる中、チップ配線と積層化はパフォーマンス向上と省電力化の鍵を握っています。アプライド マテリアルズが発表した最新のインテグレーテッドマテリアルズソリューションは、低抵抗の銅配線を新たにオングストロームノードにまで微細化するとともに、最新のLow-k(低誘電率)絶縁材料によりキャパシタンス低減と材料強度を両立させ、より高度な3D積層を可能にします」

ムーアの法則に準じた従来のスケーリングが背負う物理的制約を克服

現在の最先端ロジックチップには数百億個ものトランジスタが搭載され、これらを相互接続する微細な銅配線は全長60マイル(約100キロメートル)以上にも及びます。チップ内の各層の配線は、まず絶縁材料の薄膜に回路状の溝(トレンチ)をエッチングし、そこに銅を充填して作られます。Low-k絶縁膜と銅の組み合わせは、過去数十年にわたって配線工程の業界標準の座を占め、世代が代わるごとにスケーリング、パフォーマンス、電力効率を向上させてきました。

しかし業界が2nm以降への微細化を進めるにつれて、絶縁材料の薄化によるチップの機械的強度不足、銅線の狭小化がもたらす電気抵抗の急増、そしてこれに伴うチップパフォーマンスの低下や電力消費の増加といった課題が生じてきました。

改良されたLow-k絶縁材料で配線抵抗を低減、3D積層チップを高強度化

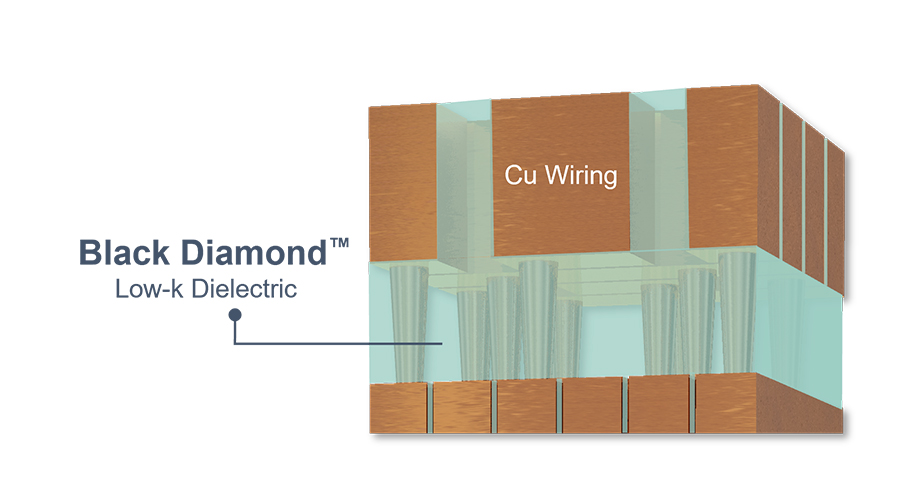

アプライド マテリアルズのBlack Diamond™は数十年にわたって業界をリードしてきました。誘電率定数(k値)が低く、電荷の蓄積を抑えるよう加工されたこの薄膜材料で銅線を覆うことにより、電力消費の増大と電気信号間の干渉を抑えることができます。

アプライド マテリアルズは本日、このBlack Diamondの改良版を発表しました。当社のProducer™ Black Diamond™ PECVD*ファミリーに新たに加わったこの薄膜材料は、最小k値をさらに引き下げて2nm以降への微細化に対応するほか、機械的強度の向上をもたらし、3Dロジックとメモリのより高度な積層化を進める半導体メーカーやシステム会社の重要課題に応えます。

この最新Black Diamond技術は、大手ロジック/DRAMチップメーカー各社で採用が進んでいます。

新たな二元金属ライナーで極細銅線を実現

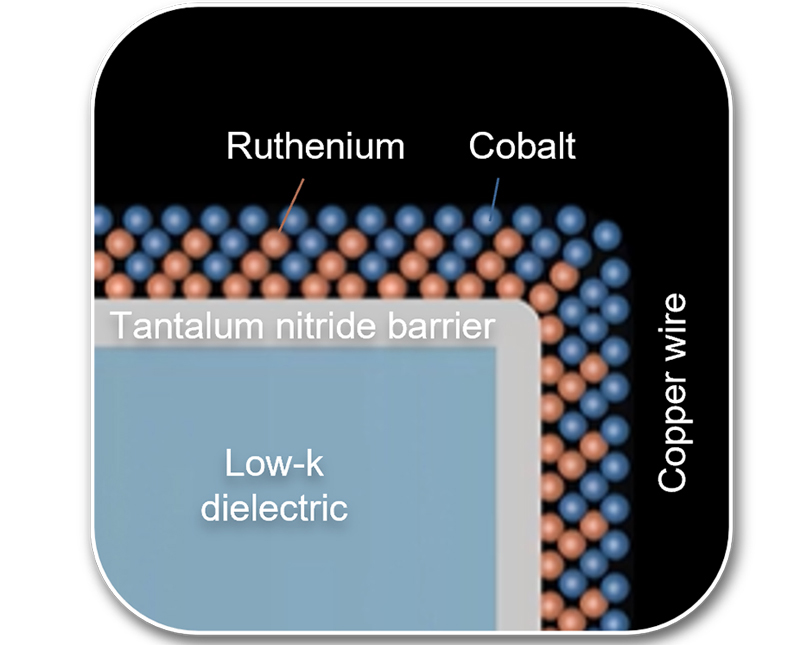

チップ配線の微細化工程では、まずLow-k膜の各層にエッチングでトレンチを設け、次に銅がチップ内にマイグレートしないようバリア層を成膜し、歩留まり低下を防ぎます。さらに、続くリフロー成膜工程で銅が確実に定着するようバリア上にライナーを塗布した後、残された空隙に徐々に銅を充填していきます。

この工程のまま配線をさらに微細化しようとしても、配線に利用できる空間の相当部分がバリアとライナーにとられてしまうため、残されたスペースに低抵抗かつボイドフリーの銅配線を設けるのは物理的に困難となってきました。

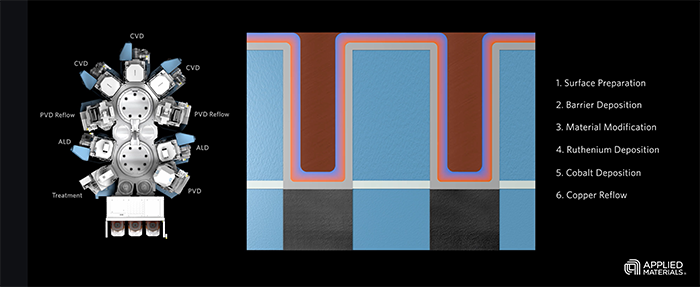

アプライド マテリアルズが本日発表した最新のインテグレーテッド マテリアルズ ソリューション(IMS™:Integrated Materials Solution™)は、1台の高真空システムに6つの異なるテクノロジーを統合します。その1つが、業界初となる材料の組み合わせを用いて銅配線の微細化を2nmノード以降へと進める技術です。このソリューションはルテニウムとコバルトを組み合わせた二元金属(RuCo)を用い、ライナー厚を33%減らして2nmにするとともに、表面特性を改良してボイドフリーの銅リフローを可能にし、電線抵抗を最大25%引き下げてチップのパフォーマンスと消費電力を改善します。

新発表のApplied Endura™ Copper Barrier Seed IMS™ with Volta™ Ruthenium CVD*は、大手ロジックメーカー各社に採用され、3nmノードに向け出荷を開始しました。このテクノロジーをアニメーションで紹介するビデオはこちらからご覧いただけます。

お客さまのコメント

Samsung Electronicsの副社長 兼 ファウンドリディベロップメントチーム責任者、Sunjung Kim氏は次のように語っています。「パターニング技術の高度化に伴い継続的なデバイス微細化が進む一方で、配線抵抗、キャパシタンス、信頼性などの面ではまだ重要課題が残されています。当社はこうした課題の克服を目指し、各種のマテリアルズ エンジニアリング イノベーションを採用して、微細化のメリットを最先端ノードにも拡張していきます」

TSMCのエグゼクティブバイスプレジデント 兼 共同最高執行責任者、Y.J. Mii氏は次のように話しています。「半導体業界がAIコンピューティングの持続可能な成長を支えるためには、エネルギー効率のパフォーマンスを大幅に改善する必要があります。配線抵抗を低減する新たな材料は、システム全体のパフォーマンスと消費電力の改善をもたらす他のイノベーションとともに、半導体業界で重要な役割を果たすでしょう」

配線関連の事業機会が拡大

アプライド マテリアルズはチップ配線プロセス技術で業界をリードしています。7nmノードから3nmノードへ移行した際、配線ステップ数は約3倍に増え、当社の配線における市場機会は新規着工ファブの月産投入ウェーハ10万枚あたり10億ドル以上増え、約60億ドルに達しました。今後は裏面電源供給の導入に伴い、チップ配線に関連する当社の事業機会は月産投入ウェーハ10万枚あたりさらに10億ドル増え、70億ドルに達する見通しです。

チップ配線に関連する新製品と、将来のAIチップ製造に向けたマテリアルズ エンジニアリングのその他のイノベーションについては、アプライド マテリアルズがSEMICON West 2024で主催するTechnology Breakfastで取り上げる予定です。このイベントで行われるプレゼンテーションおよびその他資料は、アプライド マテリアルズのウェブサイト(https://ir.appliedmaterials.com)で2024年7月9日火曜日(米国東部時間午前9時頃、米国太平洋時間午前6時頃、日本時間午後10時頃)からご覧いただけます。

*PECVD:プラズマ化学気相成長

*CVD:化学気相成長

将来予想に関する記述について

本プレスリリースには、当社の新しい製品と技術から見込まれる恩恵、当社の事業や市場の成長予測とトレンド、業界見通しと需要拡大要因、テクノロジーの遷移など将来の見通しに関する記述や、過去の事実には該当しないその他の記述が含まれています。こうした記述やその前提をなす仮定はリスクや不確定要素に左右され、将来のパフォーマンスを保証するものではありません。こうした記述が明示ないし黙示する帰結と実際の結果の間に大きな違いをもたらし得る要因としては、当社の新しい製品と技術から見込まれる恩恵の不実現;半導体および当社製品・テクノロジーへの需要;技術や生産設備に対する取引先企業のニーズ;新たな革新的テクノロジーの導入とテクノロジー移行のタイミング;既存ならびに新開発の製品に対する市場の受容性;当社がテクノロジーに関する知的財産権を取得ならびに保護する能力;適用される法律、規則、規制の遵守を当社が確保する能力;および当社が証券取引委員会(SEC)に提出する書類(最新のForm 10-Qおよび8-K報告書を含む)に記載しているその他のリスクや不確定要素などがあります。将来の見通しに関する記述はすべて本プレスリリース発表時点における経営陣の推定、予測、仮定に基づくものです。アプライド マテリアルズは将来の見通しに関する記述を更新する義務を負っておりません。

アプライド マテリアルズ(Nasdaq: AMAT)は、マテリアルズ エンジニアリングのソリューションを提供するリーダーとして、世界中のほぼ全ての半導体チップや先進ディスプレイの製造に寄与します。原子レベルのマテリアル制御を産業規模で実現する専門知識により、お客さまが可能性を現実に変えるのを支援します。アプライド マテリアルズはイノベーションを通じてよりよい未来を可能にします。

詳しい情報はホームページwww.appliedmaterials.com でもご覧いただけます。

*************************************************************************

このリリースは7月8日、米国においてアプライド マテリアルズが行った英文プレスリリースをアプライド マテリアルズ ジャパン株式会社が翻訳の上、発表するものです。

アプライド マテリアルズ ジャパン株式会社(本社:東京都、代表取締役社長:中尾 均)は1979年10月に設立。大阪支店、川崎オフィスのほか全国各地にサービスセンターを置き、日本の顧客へのサポート体制を整えています。

このリリースに関するお問い合わせは下記へメールにてご連絡をお願いいたします。

アプライド マテリアルズ ジャパン株式会社 広報宛メール Applied_Materials_Japan@amat.com

ホームページ: www.appliedmaterials.com/ja

Applied Materials’ Latest Integrated Materials Solution™ Extends Copper Wiring to 2nm and Beyond

Applied Materials’ new Endura™ Copper Barrier Seed IMS™ with Volta™ Ruthenium CVD combines six different technologies in one high-vacuum system, including an industry-first combination of materials that enables chipmakers to scale copper wiring to the 2nm node and beyond.

Combining Ruthenium and Cobalt Improves Chip Performance and Power Consumption

With the semiconductor industry’s first use of ruthenium in high-volume production, Applied Materials' new binary metal combination of ruthenium and cobalt (RuCo) enables copper chip wiring to be scaled to the 2nm node and beyond and reduces electrical line resistance by as much as 25 percent.

Enhanced Black Diamond™ Reduces Interconnect Resistance and Strengthens Chips for 3D Stacking

Applied Materials today introduced an enhanced version of the company’s Producer™ Black Diamond™ PECVD dielectric film. This new material enables chip scaling to 2nm and below, while offering increased mechanical strength to help take 3D logic and memory stacking to new heights.